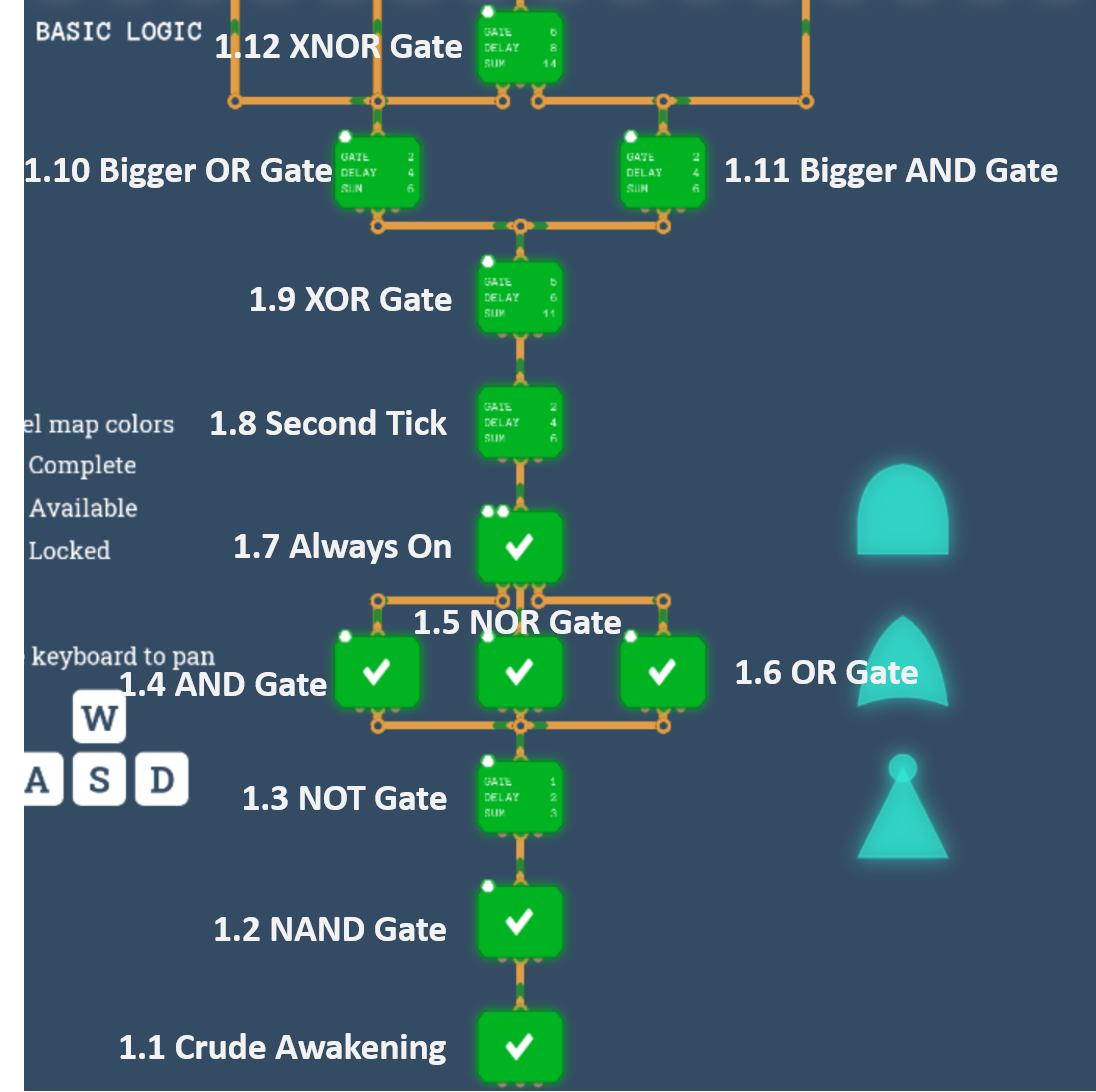

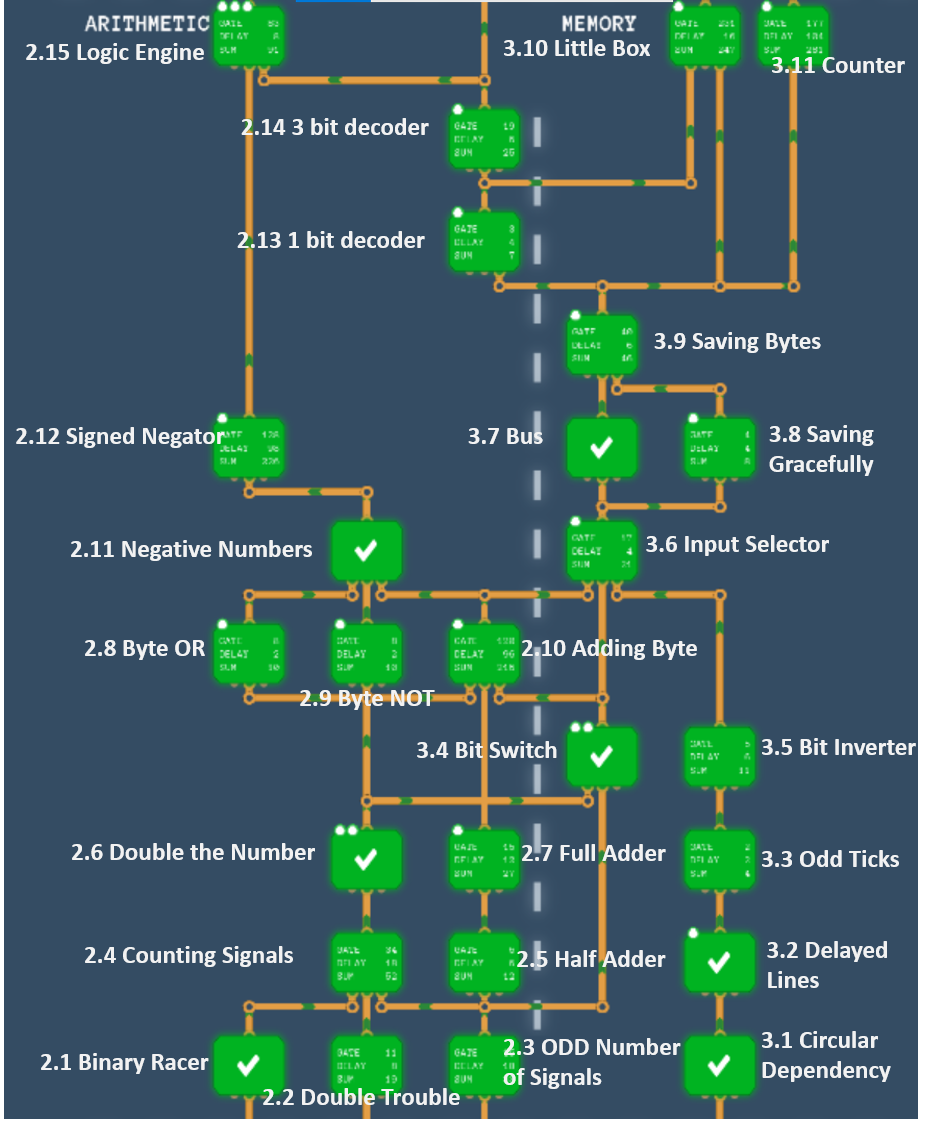

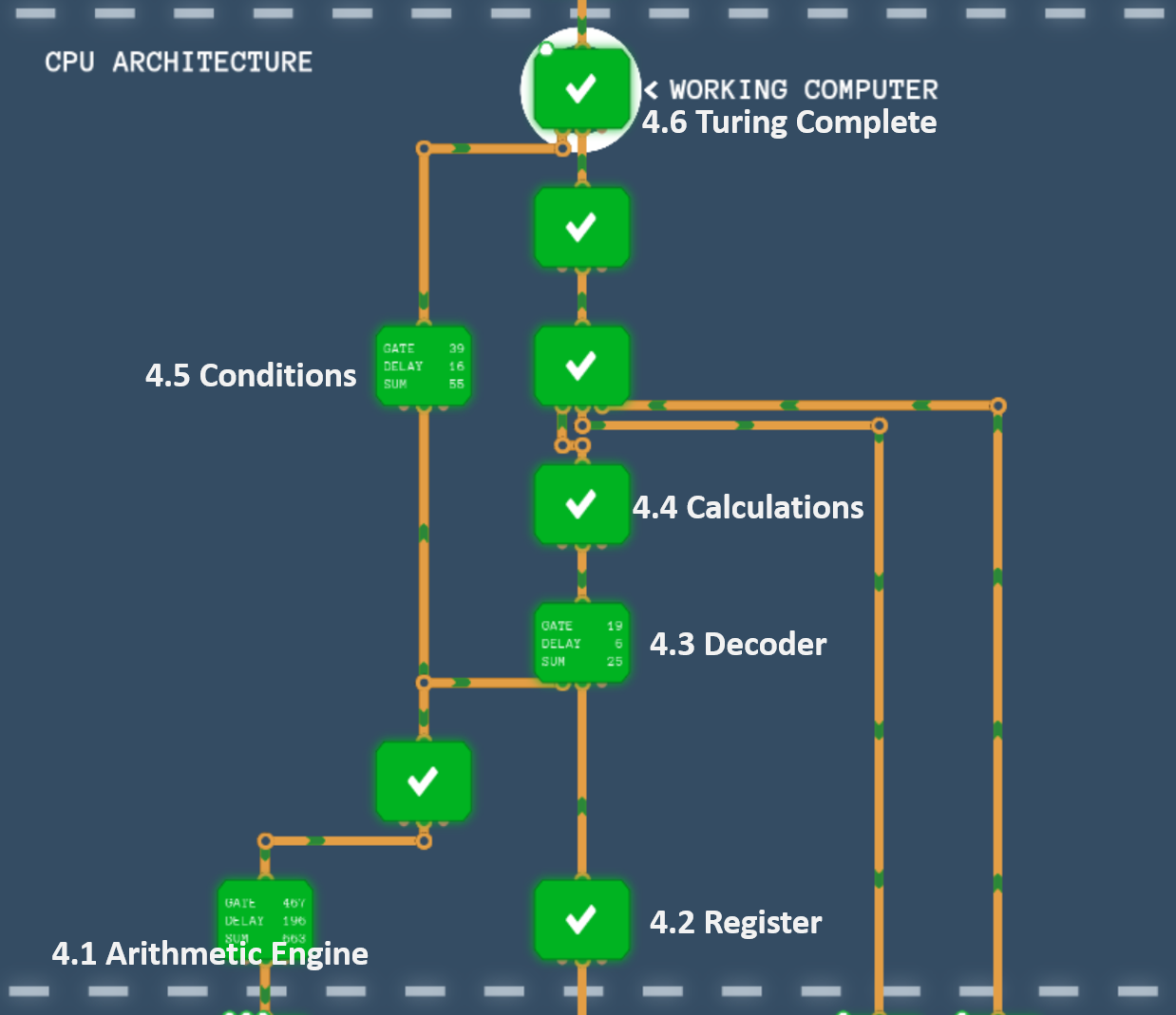

CPU Architecture

从NAND开始构建所有基础logic gate并且最终完成一个turing complete的基础的,可编程的计算机结构。基于游戏turing complete。

Basic Logic

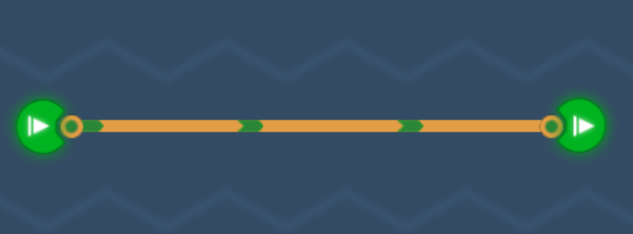

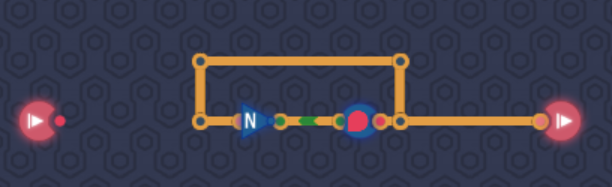

Crude Awakening

| Input | Output |

|---|---|

| 1 | 1 |

| 0 | 0 |

Input=Output

基础连接教程

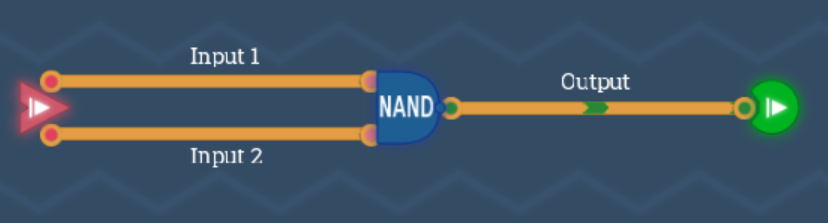

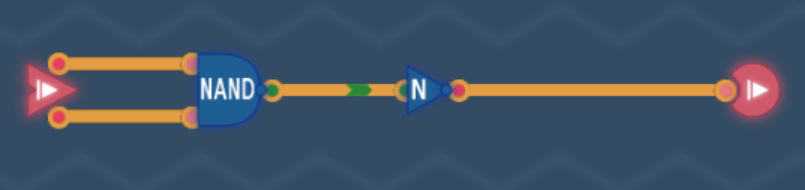

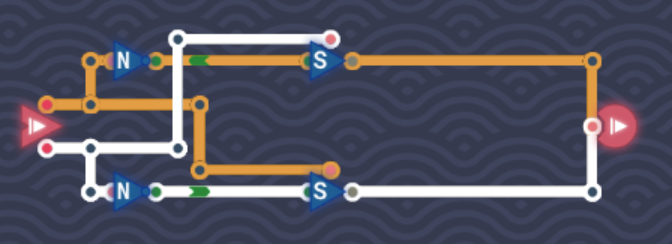

NAND Gate

| Input1 | Input2 | Output |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

(Input1*Input2)=Output

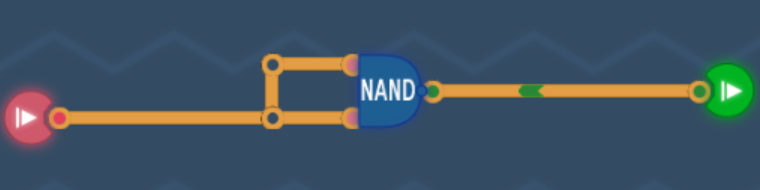

NOT Gate

| Input | Output |

|---|---|

| 1 | 0 |

| 0 | 1 |

Input’=Output

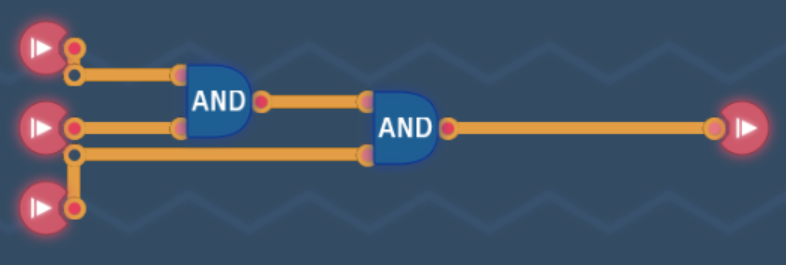

AND Gate

| Input1 | Input2 | Output |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Input1*Input2=Output

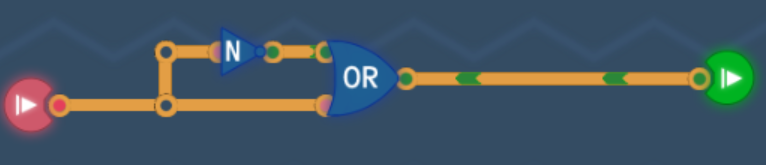

NOR Gate

| Input1 | Input2 | Output |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

(Input1+Input2)’=Output

OR Gate

| Input1 | Input2 | Output |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Input1+Input2=Output

Always On

| Input | Output |

|---|---|

| 1 | 1 |

| 0 | 1 |

1=Output

Second Tick

| Input1 | Input2 | Output |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Input1*Input2’=Output

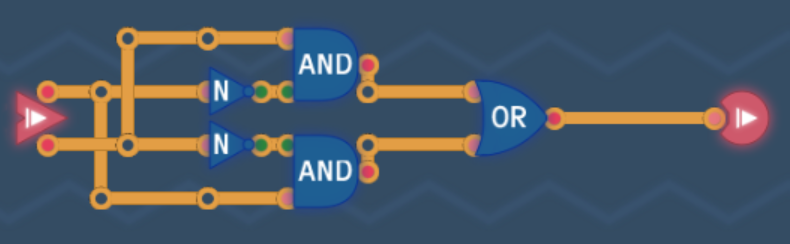

XOR Gate

| Input1 | Input2 | Output |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Input1*Input2’+Input1’*Input2=Output

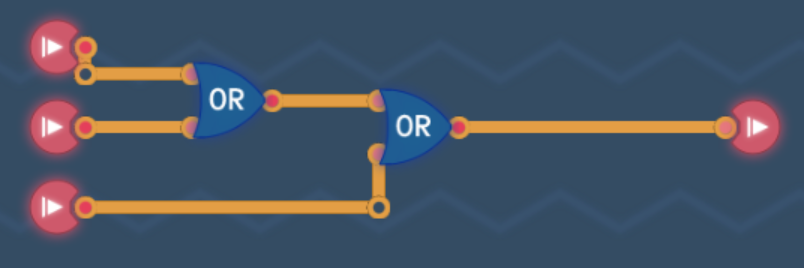

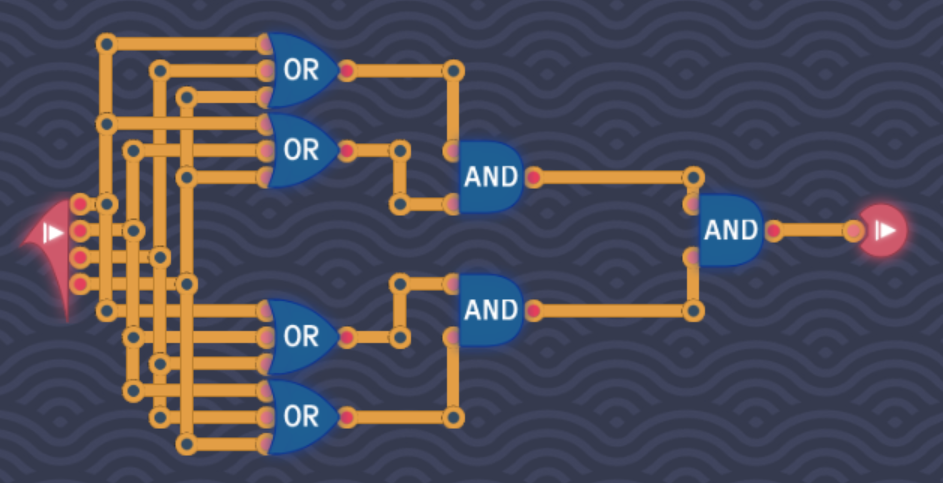

Bigger OR Gate

Input1+Input2+Input3=Output

Bigger AND Gate

Input1Input2Input3=Output

XNOR Gate

| Input1 | Input2 | Output |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

(Input1*Input2’+Input1’*Input2)’=Output

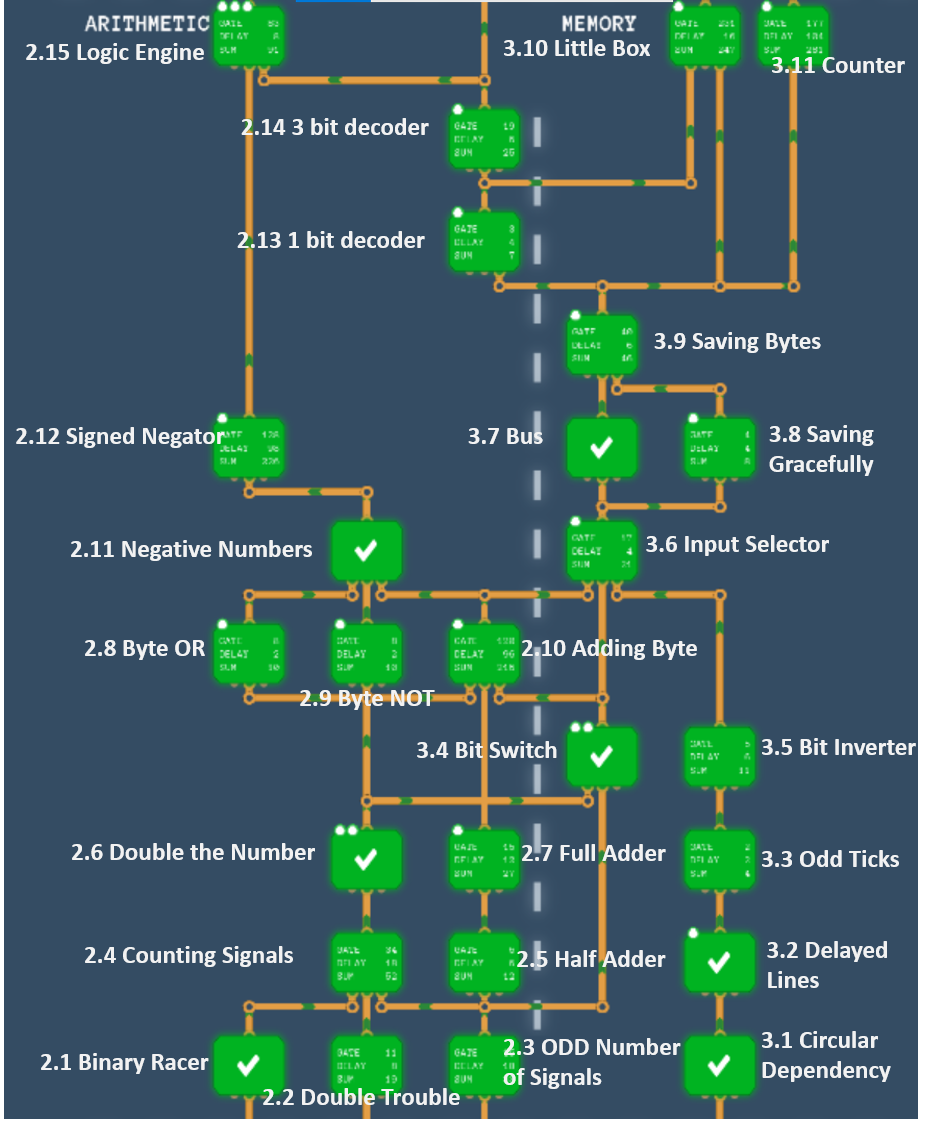

Arthmetic

Binary Racer

None

Double Trouble

输出1如果大于或等于2个inputs为1

ODD Number of Signals

输出1如果1个或3个inputs为1

Counting Signals

输出inputs为1的terminal的数量。output是3 bits输出,可为000, 001, 010, 011, 100

1.首先由ODD Number of Signals决定最后一位

2.再由Double Trouble找出大于等于2的情况,并和(3.)连接一个XOR去除找出全为1的情况

3.将4个terminals用and连接找出全为1的情况

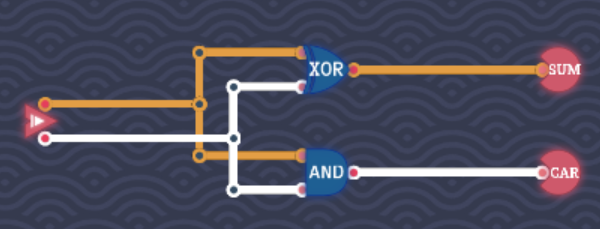

Half Adder

| Input1 | Input2 | Sum | Carry |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

统计Input True数量,只有两个Inputs的Counting Signals

Sum: 个位

Carry: 十位

Double the Number

Bits Shift Left

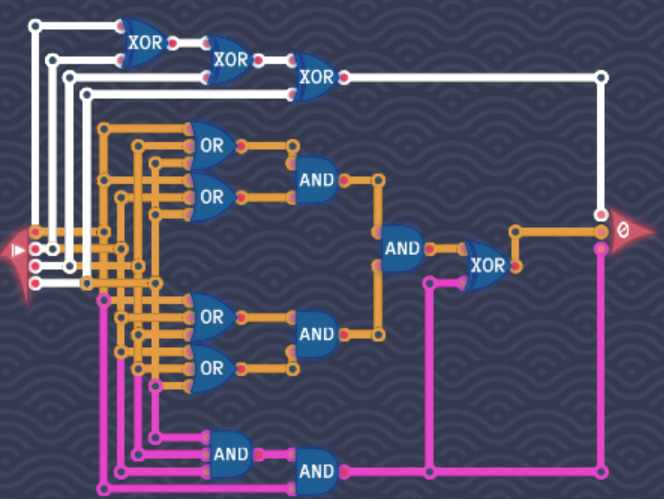

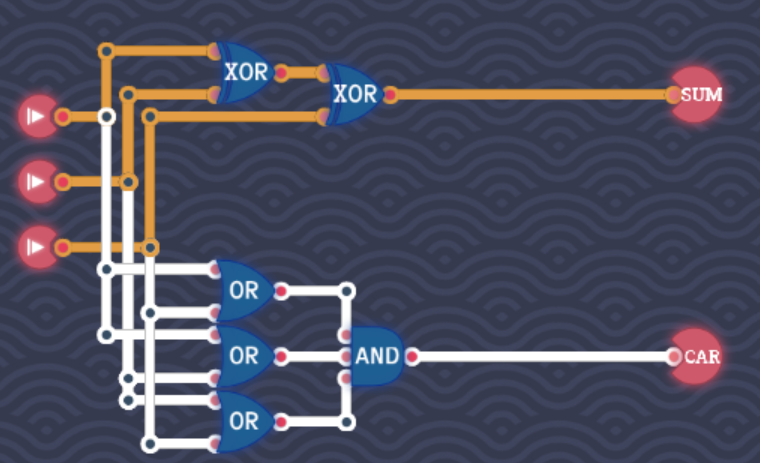

Full Adder

| Input1 | Input2 | Input3 | Sum | Carry |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

统计Input True数量,只有三个Inputs的Counting Signals

Sum: 个位

Carry: 十位

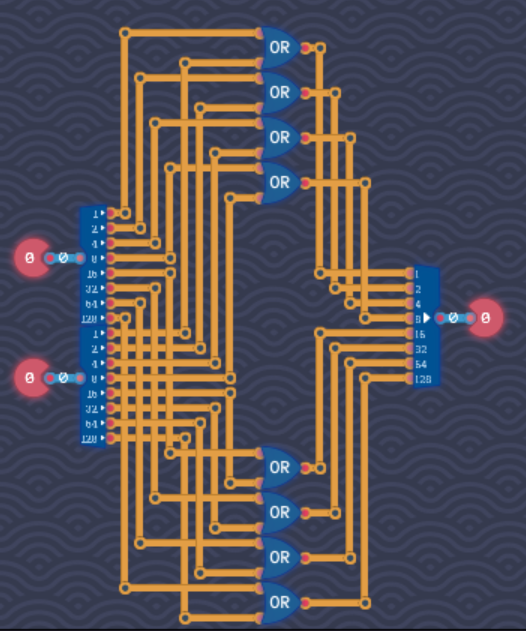

Byte OR

暴力堆叠

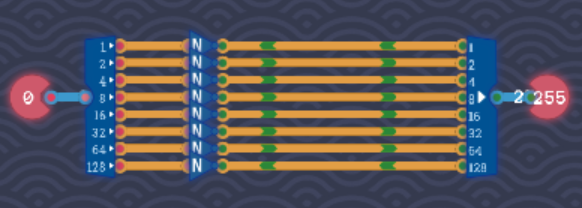

Byte NOT

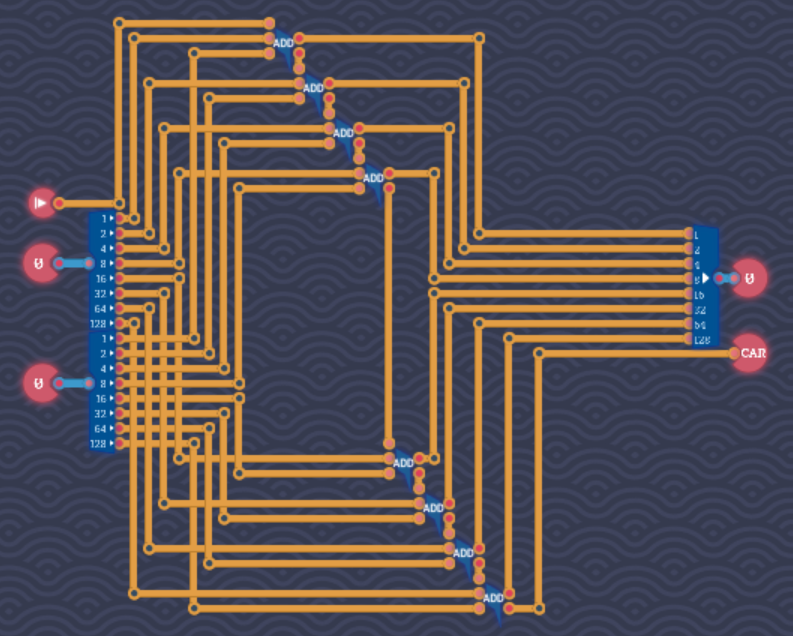

Adding Byte

Negative Numbers

None

Signed Negator

转负数

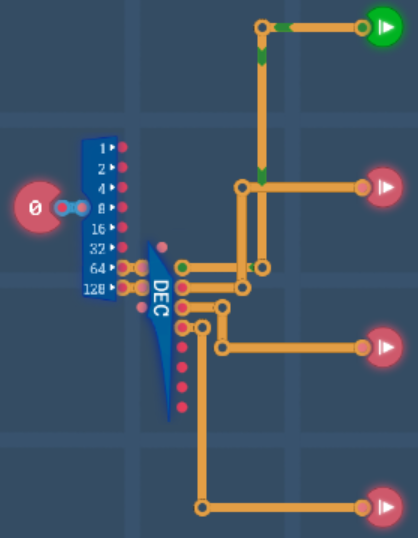

1 bit decoder

1 bit解码器,将两种情况分别用两个output terminals输出

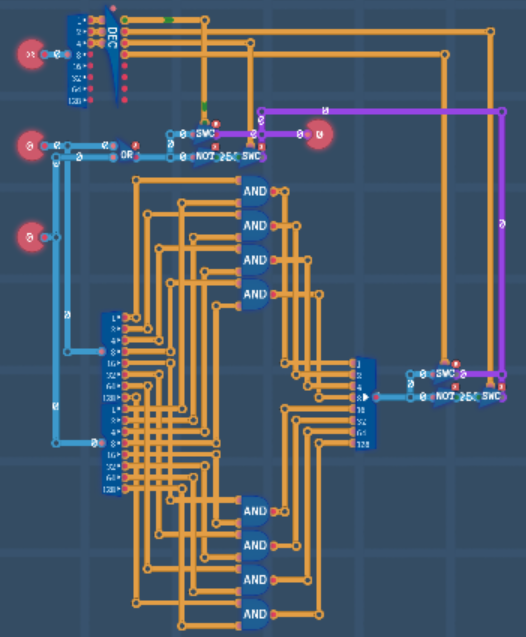

3 bit decoder

3 bit解码器,计算机设计最常用的器件之一,可以很方便的解码program coding,特别是分析opcode的指令

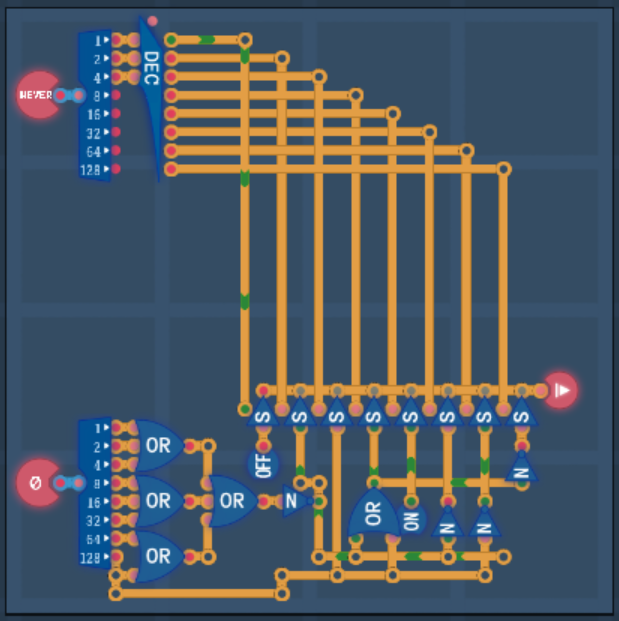

Logic Engine

3 bits解码器简单应用,用decoder控制输出的数据是or nor and nand这四种里的一种情况

Memory

Circular Dependency

None

Delayed Lines

过一个tick输出上一个tick内容

Odd Ticks

在奇数tick才会输出1

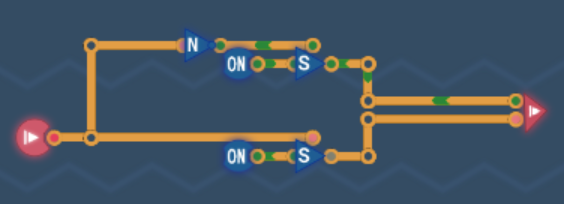

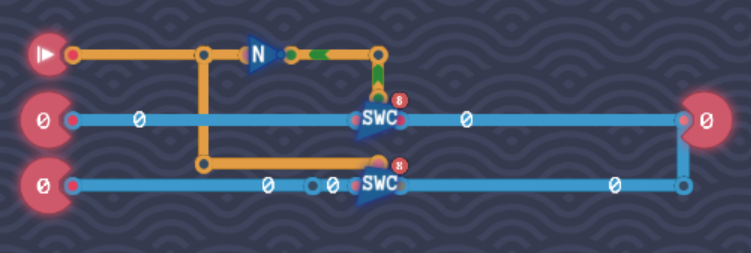

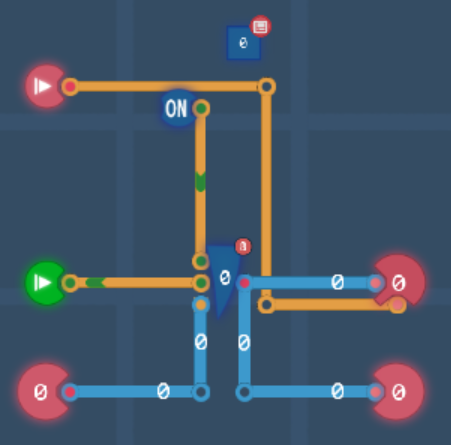

Bit Switch

使用一个可选择开关的component

Bit Inverter

只有两个inputs不一样才会输出1

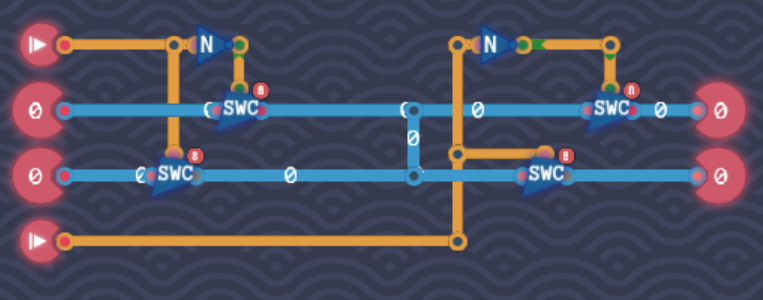

Input Selector

根据上边input bit来选择输出下边那个数据

Bus

设计一种总线来统一转递数据和控制数据传递

Saving Gracefully

上边是save,下边是value,当save为1时更新output为value的值,1 bit memory, register的基础

Saving Bytes

用1 bit memory来保存1 byte的数据

Little Box

最上边两个为loading and saving,然后是选择A/B和0/1,并最终定位到四个register中的一个,来操作saving或loading操作

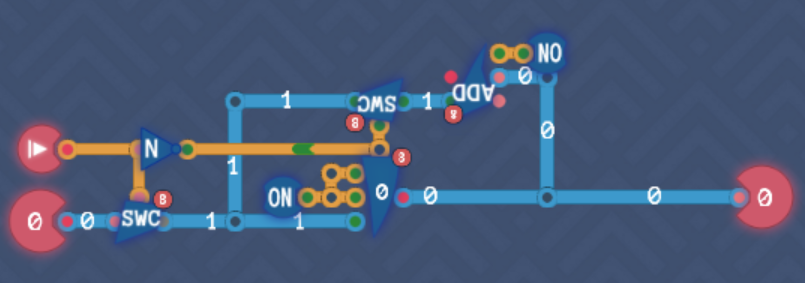

Counter

平时每过一个tick就加1,如果overwrite为1就直接写入input的数值,之后program时用来读取程序的component

CPU Architecture

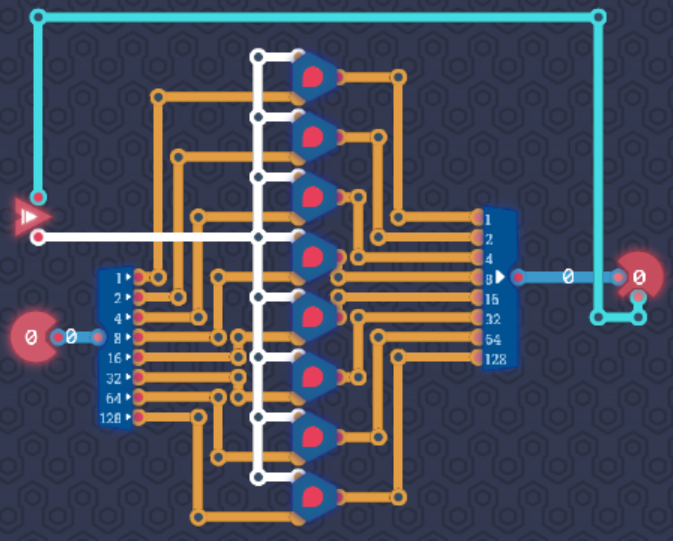

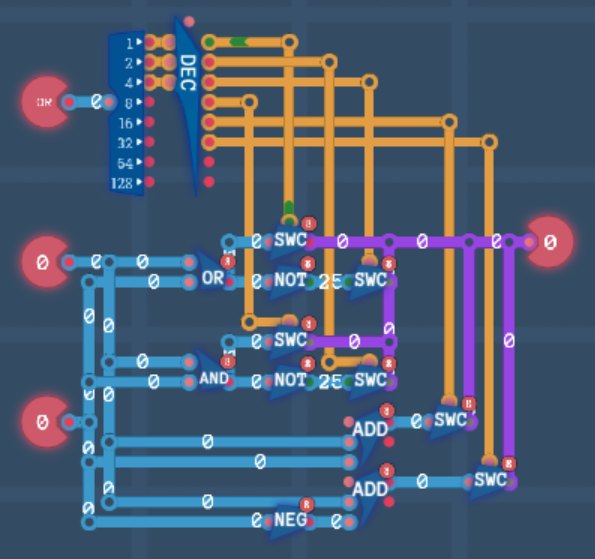

Arithmetic Engine

最上边的是1 byte输入,通过不同的输入分别输出不同的运算结果

| Input | Operation |

|---|---|

| 0 | OR |

| 1 | NAND |

| 2 | NOR |

| 3 | AND |

| 4 | ADD |

| 5 | SUB |

Register

3输入分别为loading,saving和saved value。输出的话上边的output只有在loading为1时才输出,下边在任何时候都会输出

Decoder

3 bits decoder的简单应用

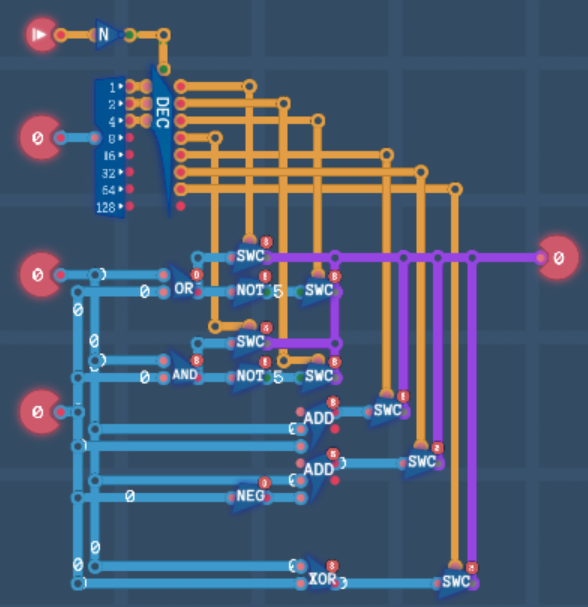

Calculations

Arithmetic Engine的扩展运用,基本一致

| Input | Operation |

|---|---|

| 0 | OR |

| 1 | NAND |

| 2 | NOR |

| 3 | AND |

| 4 | ADD |

| 5 | SUB |

| 6 | XOR |

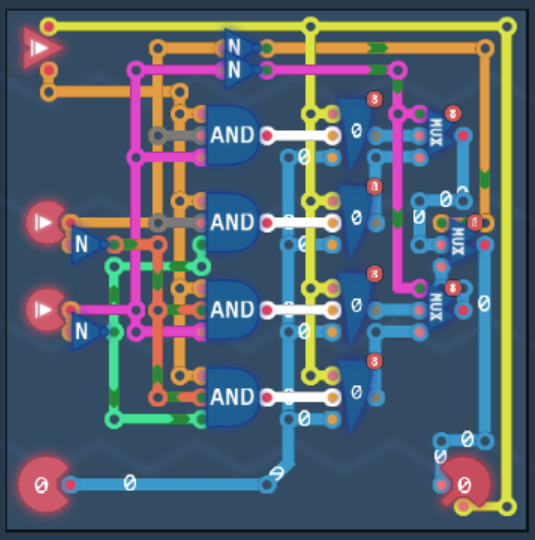

Conditions

根据上边的输入选择不同的判断条件,如果输入符合就输出1,不符合输出0。类似if的判断逻辑

| Input | Condition |

|---|---|

| 0 | NEVER(Always off) |

| 1 | =0 |

| 2 | <0 |

| 3 | <=0 |

| 4 | ALWAYS(Always on) |

| 5 | !=0 |

| 6 | >=0 |

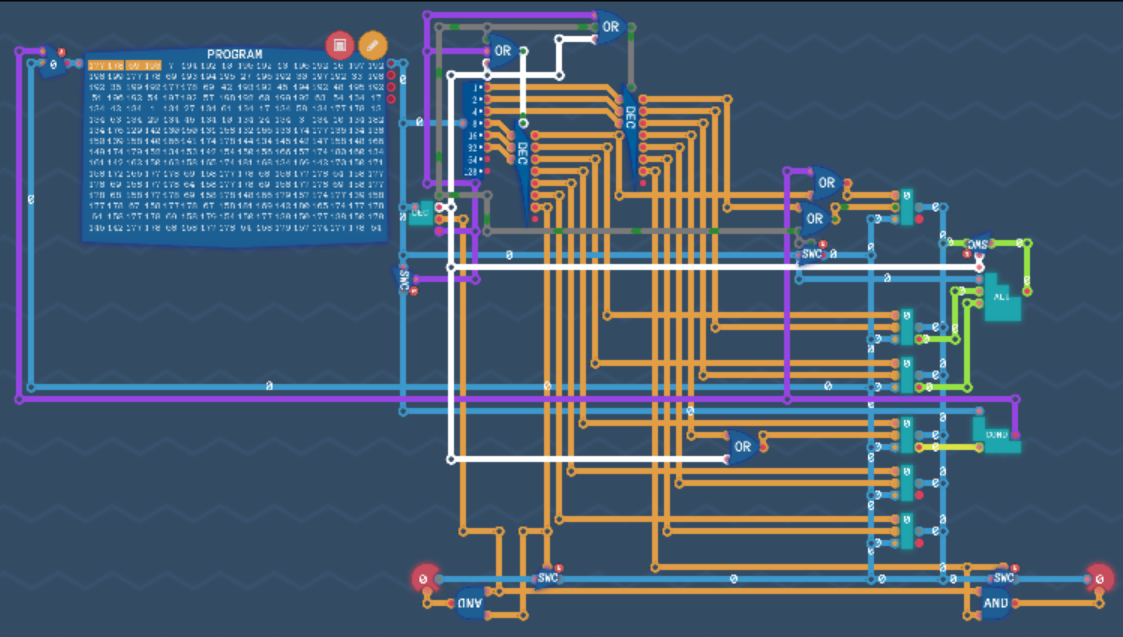

Turing Complete

一个可以编程的可运算图灵完备的结构,配备program ram,counter,6 registers,compute,condition。

任何将saving,loading,或calculation的值都会先输入到一个bus内统一调取。

每个program里的数据为1 byte,最后两位控制这个数据的类型并由DEC解码和控制:

| bits(7 and 8 bit) | type |

|---|---|

| 00 | IMMEDIATE |

| 01 | COMPUTE |

| 10 | COPY |

| 11 | CONDITION |

10

两个3 bits decoders分别控制6个registers,input and output的loading和saving操作

如指令 10 110 001 意思是将input and output 里的数据复制到reg1里

| VALUE(1-3bits for saving, 4-6bits for loading) | component |

|---|---|

| 0 | reg0 |

| 1 | reg1 |

| 2 | reg2 |

| 3 | reg3 |

| 4 | reg4 |

| 5 | reg5 |

| 6 | input and output |

00

如果为00,将直接将前6位bits写入reg0,直接disable 2个3 bits decorders,并将value直接saving进reg0内

如 00 000 010 将直接在reg0内写入数值2

注意这个方法只能最大写入2^6=64到reg0内

01

如果为01,ALU将被enabled并根据1-3 bits判断计算方式,如之前的Calculations:

| Input | Operation |

|---|---|

| 0 | OR |

| 1 | NAND |

| 2 | NOR |

| 3 | AND |

| 4 | ADD |

| 5 | SUB |

| 6 | XOR |

reg1和reg2内的数值将分别当作input1和input2,并将result自动存入reg3内

如 01 000 100 将自动把reg1和reg2内的值相加,并存储到reg3内

11

如果为11,机器将根据COND里的逻辑分析1-3 bits:

| Input | Condition |

|---|---|

| 0 | NEVER(Always off) |

| 1 | =0 |

| 2 | <0 |

| 3 | <=0 |

| 4 | ALWAYS(Always on) |

| 5 | !=0 |

| 6 | >=0 |

机器将自动读取reg3内的值输入,如果条件成立,会自动loading reg0内的值并赋值给counter来达到跳转的效果,类似if语句内达到条件就运行新语句的效果

如 11 000 100 就会一直将reg0内的值赋予counter,做到汇编内JMP的效果

program example

| Name | code |

|---|---|

| MOV | 10 000 000 |

| from_REG1 | 00 001 000 |

| to_REG1 | 00 000 001 |

| AND | 01 000 011 |

| JMP | 11 000 100 |

1 | //计算一个数除以4后的余数,可以将这个数和3进行AND操作来计算 |

一行代码可以选择将不同的命令相加来达到灵活编程的目的,如MOV+REG0+to_REG1=10 000 000+00 000 000+00 000 001=10 000 001=将reg0内的值复制到reg1